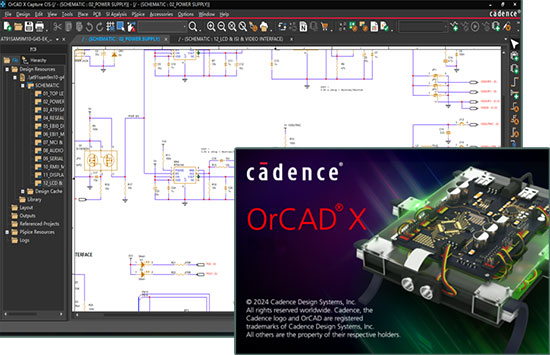

OrCAD X Capture(R) CIS

OrCAD Capture是用于创建和记录电路的最广泛使用的原理图解决方案之一。快速、简单和直观的电路设计,以及支持高度集成的设计流程,使得OrCAD Capture成为当今产品创建中最受欢迎的设计环境之一。

当今电子产品的设计不仅仅是简单地连接器件、创建符号库、将网表放到PCB中并希望得到最好的结果。元器件信息、变体设计和电路复用、层次式原理图、电路和信号完整性仿真,以及与企业数据系统的集成,都在减少您的开发时间和项目成本、提高产品可靠性和可制造性。

主要特性

- 广泛而高效的原理图输入功能确保了简单、快速、直观的原理图设计

- 层次式、复用和变体设计能力简化了复杂设计的创建

- OrCAD CIS通过推广首选零件和优化零件选择,加快设计进程,降低项目成本

- 从原理图到PCB的一致的约束管理器流程,提供无缝的约束同步

- 集成的信号完整性、模拟/混合信号设计和仿真支持

- 与OrCAD PCB SI和OrCAD PCB设计产品的双向集成

- 支持不同格式的网表,可嵌入多种EDA工具设计流程

原理图设计功能

-

原理图设计

OrCAD Capture原理图编辑器继承传统优势,提供从简单到复杂设计的快速编辑。其直观界面和丰富功能显著提升电路设计效率;

-

效率与易用性

原理图编辑器通过自动布线、上下文菜单、OLE支持、自定义着色和标签式界面等功能提升设计效率。OrCAD Capture支持层次化设计和交叉标注,便于复杂电路的连接管理;

-

智能PDF

智能PDF导出功能可创建支持器件跳转、属性识别的PDF文档,团队成员无需额外软件许可即可进行设计审查;

-

设计复用

复用已验证的现有电路可减少设计时间并确保质量,典型例子包括电源模块、射频电路设计、多通道电路和存储器;

-

FPGA设计

支持与OrCAD FPGA系统规划器的协同设计流程,可快速导入FPGA器件数据创建原理图符号。

解决方案和流程

-

元件信息系统

CIS自动将外部参数化器件数据与原理图设计数据库同步,可直接访问MRP、ERP或PLM系统中的数据;

-

设计变体

设计变体功能可管理无限电路板组装变体,无需维护重复原理图或手动编辑单个BOM;

-

PSpice仿真

集成的PSpice模拟/混合信号电路仿真器可使用同一原理图进行仿真分析和PCB布局;

-

符号编辑器

增强型符号编辑器提供精确绘图功能,支持无限撤销/重做,可为符号添加自定义图像;

-

约束管理器

集成的约束管理器提供约束驱动流程,实现原理图和PCB布局间的无缝约束同步;

-

信号完整性

集成的PSpice模拟/混合信号电路仿真器可使用同一原理图进行仿真分析和PCB布局;

-

PCB设计集成

与OrCAD PCB Editor的无缝双向集成支持原理图和电路板间的同步和交叉探测;

-

开放架构平台

可扩展和可定制的设计环境包含高度集成的Tcl/HTML5编程基础设施,可创建或增强功能和工作流程